Introduction to Transistor Flip Flops

A transistor flip flop is a type of electronic circuit that uses transistors to store a single bit of binary data. It is a fundamental building block in digital electronics and is used extensively in computer memory, registers, and other digital systems that require data storage.

Flip flops are sequential logic circuits, meaning their output depends not only on the current inputs, but also on the previous state of the outputs. This allows flip flops to “remember” and hold data, even when the inputs change. In contrast, combinational logic circuits like AND gates and OR gates have outputs that depend only on the current combination of inputs.

The ability to store and hold data makes the flip flop a key component in synchronous digital systems. Flip flops are triggered by a clock signal, allowing them to synchronize the flow and timing of data within a digital circuit. On each clock pulse, the flip flop samples and stores the value of its inputs. The stored data is then held stable and available on the outputs until the next clock pulse.

History and Development of Flip Flops

The concept of the flip flop dates back to the early days of digital computing in the mid-20th century. In 1918, William Eccles and Frank Jordan described a bistable multivibrator circuit using vacuum tubes, now known as the Eccles-Jordan trigger circuit. This was an early precursor to the modern flip flop.

With the invention of the transistor in 1947 and its subsequent adoption in digital circuits, transistor-based flip flops became the norm. In 1955, Evert Seevinck and Eibert Hoekstra proposed the emitter-coupled RS flip flop using bipolar junction transistors (BJTs). This design formed the basis for many future transistor flip flop circuits.

Over the decades, various types of transistor flip flops were developed to address different needs in digital systems. The D flip flop and JK flip flop added control inputs to address limitations of the original RS type. Master-slave configurations were devised to prevent output instability. And as metal-oxide-semiconductor (MOS) technology matured, MOSFET-based flip flops became predominant, offering advantages in power consumption, circuit density, and speed.

Today, transistor flip flops are ubiquitous in the integrated circuits that power our computers, smartphones, and countless other digital devices. Advances continue to be made to improve their performance, energy efficiency, and scalability as IC manufacturing processes reach ever smaller nanometer nodes.

How Transistor Flip Flops Work

At its core, a transistor flip flop is made up of a feedback loop that allows the circuit to have two stable states. These states can be used to represent the two values of a binary bit, 0 and 1. Once the flip flop is put into one of these states, it will remain there until a triggering input causes it to change to the other state.

Basic RS Flip Flop

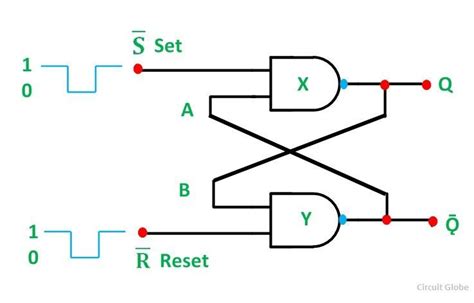

The most basic type of flip flop is the RS (Reset-Set) flip flop. It has two inputs labeled R and S, and two outputs labeled Q and Q’ (Q-complement). The outputs are always in opposite states, so if Q is 1, then Q’ is 0, and vice versa.

Here’s how the RS flip flop works:

- When input R is 1 and S is 0, the flip flop resets. Output Q becomes 0 and Q’ becomes 1.

- When input S is 1 and R is 0, the flip flop sets. Output Q becomes 1 and Q’ becomes 0.

- When both R and S are 0, the flip flop holds its previous state. The outputs remain unchanged.

- The state where both R and S are 1 is avoided as it leads to an invalid condition.

The following truth table summarizes the behavior of the RS flip flop:

| R | S | Q | Q’ |

|---|---|---|---|

| 0 | 0 | Q | Q’ |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | invalid |

A simple transistor implementation of the RS flip flop uses two NPN BJTs arranged in a cross-coupled configuration:

[Diagram of BJT RS flip flop circuit]

When an input goes high, it turns on its corresponding transistor which then pulls the opposite side low through the collector-emitter path. This feedback maintains the state after the input returns low. Resistors are used to limit current and ensure proper voltage levels.

Clocked Flip Flops

The RS flip flop by itself is transparent, meaning its outputs can change immediately when the inputs change. In synchronous sequential systems, this is not desirable as we want changes to occur only on controlled clock pulses. Clocked variations of the flip flop are used to achieve this.

The most common clocked flip flop is the D flip flop. It has a single data input D and a clock input CLK, along with the Q and Q’ outputs. On the rising edge of the clock, the flip flop samples the value of D and transfers it to the outputs. The outputs then remain stable regardless of further changes in D until the next clock edge.

A positive-edge-triggered D flip flop can be constructed using a master-slave arrangement of two D latches (simple gated D flip flops):

[Diagram of transistor D flip flop (master-slave)]

On the low phase of the clock, the master latch is open and the slave latch is closed. The master tracks the input D while the slave holds the previous value. On the rising clock edge, the master closes, capturing the current input value, and the slave opens, allowing the stored value to reach the outputs. This ensures that the output only changes on clock edges and prevents any intermediate glitches.

Other types of clocked flip flops include the JK flip flop and T flip flop. These have additional control inputs that allow more flexibility in toggling the stored bit under different input conditions.

Applications of Flip Flops

Flip flops are essential components in a wide range of digital systems. Some key applications include:

Data Storage

Flip flops are the building blocks of static RAM (SRAM) in computer memory. Each SRAM cell uses a pair of cross-coupled inverters (effectively forming an RS latch) to store a bit. Clocked flip flops are used to interface the memory with the synchronous logic of the CPU.

Flip flops are also used to store data in registers, which are small high-speed memory units within the CPU for holding temporary data, addresses, and instructions. Registers consist of an array of flip flops, one for each bit of the register’s width.

Frequency Division

Flip flops can be used to divide the frequency of a clock signal by powers of two. A simple divide-by-two circuit uses a T flip flop with its Q’ output fed back to its T input. On each clock pulse, the flip flop toggles its state, resulting in an output frequency that is half the input frequency. Ripple counters with multiple flip flops in series can divide frequencies by larger factors.

Synchronization and Timing

Flip flops play a key role in synchronizing data flow and timing in digital circuits. By triggering flip flops with a common clock signal, data can be made to move through the system in coordinated steps, with each flip flop holding its value for a full clock cycle. This prevents timing errors and ensures that data arrives at the intended destination at the right time.

Flip flops are also used in pipeline registers, which are inserted between stages of combinational logic to break up long paths and improve overall system clock speed.

Debouncing

Mechanical switches and buttons can produce spurious transitions when pressed or released due to bouncing of the contacts. If used directly as an input to sequential logic, this can cause unwanted multiple triggering. A flip flop can be used to debounce the switch signal by waiting for the bounces to settle before registering the input.

Shift Registers

Shift registers are a type of sequential logic circuit that uses flip flops to shift data in a serial manner. Data is input one bit at a time and shifted through the register with each clock pulse. Shift registers are commonly used for serial-to-parallel and parallel-to-serial data conversion, delay lines, and sequence generators.

Flip Flop Timing Considerations

The proper operation of flip flops in a synchronous system depends on meeting certain timing requirements. Key timing parameters for flip flops include:

- Setup Time: The minimum time before the active clock edge that the data input must be stable to ensure reliable capture.

- Hold Time: The minimum time after the active clock edge that the data input must remain stable to avoid capturing the wrong value.

- Propagation Delay: The time from the active clock edge to the appearance of the captured data on the outputs.

- Clock-to-Output Delay: The time from the active clock edge to the appearance of the output data, assuming the data input was stable for the setup time before the clock edge.

Violating the setup or hold time requirements can lead to metastability, where the flip flop enters an unstable state and its output may oscillate unpredictably before settling to a valid level. This can cause system glitches and failures.

To avoid timing issues, designers must carefully analyze and control the timing paths in their circuits. This involves accounting for worst-case propagation delays, minimizing clock skew, and providing sufficient margins for setup and hold times. Timing analysis tools and simulation are used to verify that all timing constraints are met.

Advanced Flip Flop Designs

As VLSI technologies have advanced, flip flop designs have evolved to meet the increasing demands for speed, power efficiency, and robustness. Some advanced flip flop designs include:

-

Sense Amplifier Flip Flops (SAFF): These use a differential sense amplifier stage to quickly amplify small input differences and reduce the setup time. SAFFs can operate at high speeds but have increased complexity.

-

Pulse-Triggered Flip Flops: Rather than using a level-sensitive clock, these flip flops are triggered by a short pulse generated on the clock edge. This allows for a shorter transparency period and reduces power consumption.

-

Dual-Edge Triggered Flip Flops: These flip flops can capture data on both the rising and falling edges of the clock, effectively doubling the data throughput without increasing the clock frequency.

-

Scan Flip Flops: These include additional circuitry (multiplexers) to support scan-based testing. In test mode, scan flip flops are connected in a serial chain, allowing test patterns to be shifted in and out for fault detection.

Conclusion

Transistor flip flops are a fundamental building block in digital electronics, providing the ability to store and synchronize binary data. From basic RS latches to advanced pulse-triggered designs, flip flops have evolved to meet the ever-increasing demands of modern digital systems.

As VLSI technologies continue to scale and push the limits of performance, power efficiency, and circuit density, innovative flip flop designs will play a critical role in enabling the next generation of computing and communication devices. Understanding the principles and applications of transistor flip flops is essential for anyone involved in digital system design.

FAQ

Q1: What is the difference between a latch and a flip flop?

A1: A latch is a simple gated storage element that is level-sensitive, meaning its output can change whenever the enable input is asserted. A flip flop, on the other hand, is edge-triggered and only changes its output on a specific clock edge (usually rising). Flip flops are used for synchronous systems while latches are used in asynchronous designs.

Q2: What happens if the setup or hold time of a flip flop is violated?

A2: Violating the setup or hold time can cause the flip flop to enter a metastable state where its output is unstable and may oscillate before settling to a valid level. This can lead to system glitches and unreliable behavior. In some cases, the metastability may propagate to other parts of the circuit and cause failures.

Q3: How does a master-slave flip flop work?

A3: A master-slave flip flop consists of two gated D latches (simple D flip flops) connected in series. The first latch (master) is enabled during the low phase of the clock and captures the input data. The second latch (slave) is enabled during the high phase and holds the data captured by the master. This arrangement ensures that the output only changes on rising clock edges and prevents transparency.

Q4: What is the advantage of using a sense amplifier flip flop (SAFF)?

A4: SAFFs use a differential sense amplifier stage to quickly amplify small differences in the input signals and produce a full-swing output. This allows for reduced setup times and faster operation compared to conventional flip flop designs. However, SAFFs have increased complexity and may consume more power.

Q5: How can flip flops be used for frequency division?

A5: A T flip flop with its Q’ output fed back to its T input forms a divide-by-two circuit. On each clock pulse, the flip flop toggles its state, resulting in an output frequency that is half the input frequency. Multiple flip flops can be cascaded in a ripple counter arrangement to divide frequencies by larger powers of two (4, 8, 16, etc.).

No responses yet